#2 BIT GRAY CODE COUNTER VERILOG CODE FULL#

Write pointer and read pointer both are pointing to same address location because MSB is not used for addressing FIFO it is to test full and empty condition. Hence when counter is incremented, only MSB (extra bit) changed and remaining address pointer bits remained as it is. Remember that earlier count was 0_1000 (=15). On the next write operation 5 bit gray counter will be incremented and the count is 1_1000 (=16).

Now both pointers are pointing towards 15 th location i.e. If the MSBs different and remaining all bits are equal then it is FIFO full condition.Ĭonsidering the case wherein all FIFO locations except last one are written and then same number of locations is read. With this technique if including MSB both pointers are same then it is an FIFO empty condition.

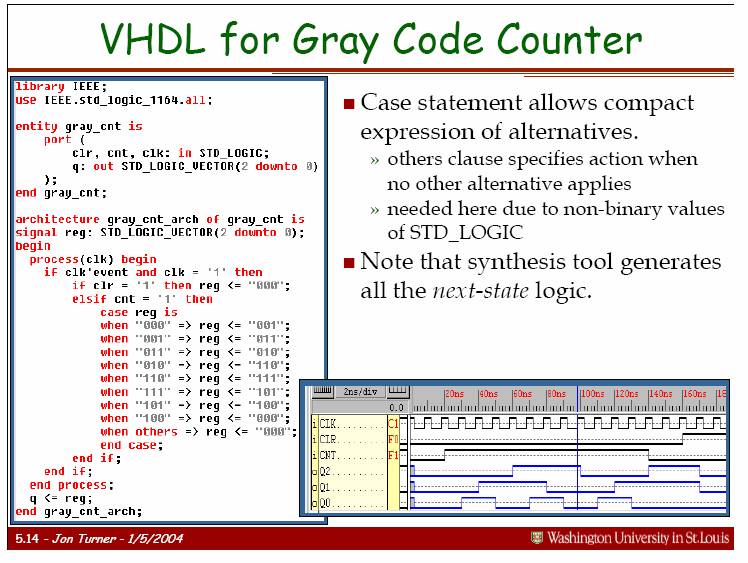

Thus if MSBs of both pointers are same it means that both pointers have wrapped else write pointer has wrapped one more time than read pointer. For read pointer also same treatment is given. Thus when write pointer increases over the final FIFO address the unused bit (MSB bit) toggles and resets remaining bits to zero. Out of this 5 bit only 4 bits are used to address 16 memory locations, while the MSB is used to detect the wrap around conditions and pointer comparisons. Thus, instead of using a 4-bit counter use 5 bit counter. To avoid this one extra bit is added to both pointers. Since read pointer is still in first location, after the wrap around of full pointer they both become equal asserting false empty condition. Recall the wrap around condition of full pointer after complete write operation of FIFO. 0 to 7) are mirror image of the second half of the number (i.e. Because of this minimized error gray counters are generally used as FIFO pointers.Ĭareful observation of 4 bit gray counter values reveal that first half of the numbers (i.e. Metastability condition on one bit causes +/- 1 count error that is better compared to +/-8 count error in binary pointers. Gray pointers too have problem of metastability while synchronizing with other clock domains but it is minimized by the fact of one bit change. to say that unlike binary numbers only one bit changes from one count to another count. Gray numbers are unidistance numbers i.e. Original clock domain resamples another count value.Īsynchronous FIFO Pointers Using Gray Counters Upon the receipt of “ready” signal other clock domain receives the count values and sends back a synchronized acknowledgement. Binary count values from original clock domain is sampled and held in holding register and a “ready” signal is passed to other clock domain. This uses handshaking signals to communicate between synchronizer and the clock domain. One way to counter this problem is to use holding register for synchronization. This is the biggest drawback of using binary counters as FIFO pointers. The pointer value synchronized with other clock domain may become entirely different than intended. This metastable state can be resolved to any four-bit count value prediction of which is almost impossible. If the synchronization clock edge becomes active in between the transition of binary bits, say, 0111 to 1000, then metastability can occur with any of the four bits or with all the bits.

Then changing bits (nothing but pointers) has to be synchronized with the other clock domains to generate empty and full condition. In worst case all 4 bits can change simultaneously like 0111 to 1000. For example bits changing from 0001 to 0010 are 2. Number of bits changing from one count to another count can be more than one. Hence to address these 16=2 4 locations we need 4 bit counter.( actually we need to design 5 bit counter….why…? we will see later !) binary code patterns are not unidistance. In our case we have total 16 memory locations in the FIFO. This counter works very well in addressing FIFO. Synchronization advantages and pitfalls between the read and write clock domain is the decisive factor in choosing right counter design as pointers.Īsynchronous FIFO Pointers Using Binary Countersīinary counter is natural counter and hence easy to design and implement. Each of these methods has merits and demerits. Two types of counters are used as FIFO pointers- binary counters and Grey counters.

0 kommentar(er)

0 kommentar(er)